在過去五十多年中,從肖克萊等人發(fā)明第一個晶體管到超大規(guī)模集成電路出現(xiàn),硅半導體工藝取得了一系列重大突破,使得以硅材料為主體的CMOS集成電路制造技術為主流,逐漸成為性能價格比最優(yōu)異、應用最廣泛的集成電路產業(yè)。

如果說在亞微米/深亞微米(Sub-Micron)時代,器件的主要bottleneck在熱載流子效應(HCE: Hot Carrier Effect)以及短溝道效應(SCE: Short Channel Effect)。那么在納米(or Sub-0.1um)時代,隨著器件特征尺寸的縮小,器件內部pn結之間以及器件與器件之間通過襯底的相互作用愈來愈嚴重,出現(xiàn)了一系列材料、器件物理、器件結構和工藝技術等方面的新問題,使得亞0.1微米硅集成電路的集成度、可靠性以及電路的性能價格比受到影響。這些問題主要包括:

(1) 體硅CMOS電路的寄生可控硅閂鎖效應以及體硅器件在宇宙射線輻照環(huán)境中出現(xiàn)的軟失效效應等使電路的可靠性降低;

(2) 隨著器件尺寸的縮小,體硅CMOS器件的各種多維及非線性效應如表面能級量子化效應、隧穿效應、短溝道效應、窄溝道效應、漏感應勢壘降低效應、熱載流子效應、亞閾值電導效應、速度飽和效應、速度過沖效應等變得十分顯著,影響了器件性能的進一步改善;

(3) 器件之間隔離區(qū)所占的芯片面積隨器件尺寸的減小相對增大,使得寄生電容增加,互連線延長,影響了集成度及速度的提高。

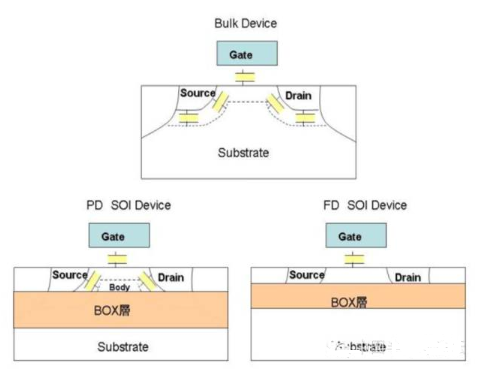

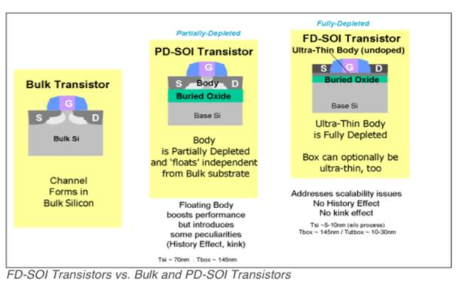

雖然深槽隔離(STI->DTI, Deep Trench Isolation)、電子束刻蝕、硅化物、中間禁帶柵電極等工藝技術能夠降低這種效應,但是只要PN結存在就會有耗盡區(qū),只要有Well就會有襯底漏電,所以根本無法解決。所以絕緣襯底上硅(Silicon-On-Insulator,簡稱SOI)技術以其獨特的材料結構有效地克服了體硅材料不足,以前最早是在well底部做一個oxide隔離層,業(yè)界稱之為BOX (Buried OXide),隔離了well的bulk的漏電,但是這種PN結依然在well里面,所以PN結電容和結漏電還是無法解決,這種結構我們稱之為部分耗盡型SOI (PD-SOI)。后來繼續(xù)演進發(fā)展到減薄oxide上面的Silicon厚度(UTSi: Ultra-Thin Si),使得它和PN結深度一樣,這樣PN結底部的耗盡層就不見了,這就是傳說中的全耗盡型SOI (FD-SOI)。目前,主流的納米制程技術都必須要采用FD-SOI技術,比如最近IBM的7nm技術就是要用SOI加上SiGe來抑制short channel effect。

講到SOI,最早的前身應該是SOS(Silicon on Sapphire, 藍寶石上硅),那個年代主要用于宇宙航天等電子器件(Satellite system),防止宇宙射線照射(radiation)導致器件失效,為啥用藍寶石主要是因為它是一種氧化鋁單晶結構,可以用它的(1-102)晶面上用異質外延方法生長一層外延層單晶硅。但是由于價格太貴無法民用商業(yè)化(commercial),后來到1980年代逐漸被SOI取代。

所以,如何在BOX(Buried OXide)上長一個Si來形成SOI wafer是一個技術挑戰(zhàn),我們前面講了如果要形成單晶層你的底部必須是單晶,如果SOS當然也可以,如果是Oxide肯定就不行了。怎么辦?如何制備SOI wafer?業(yè)界了解到的就如下三種:

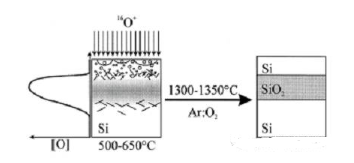

1) 注氧隔離 (SIMOX: Separation by Implantation of Oxygen),通過高劑量(~E18 氧離子/cm2)的氧離子通過高能量(200KeV)注入到Si下面,然后通過Post implant anneal來反應形成~400nm的BOX (Buried OXide)。

SIMOX做出來的SOI具有比較好的BOX均勻性,能夠通過注入能量控制BOX上面Si的厚度。但是注入退火的溫度影響Si的微結構(microstructure)。所以退火溫度一般選擇~600C。

還有個問題是BOX厚度太薄會導致SOI與襯底擊穿短路,起不到隔離效果,所以需要一道Internal OXide (ITOX)來長一層OX (~1350C),而一部分氧會穿過Si進入到Si/BOX界面反應生成ITOX來提高BOX厚度。

2) 鍵合法(Wafer bonding/mounting):將兩個氧化的Si晶片鍵合在一起,通過后續(xù)的熱處理減小鍵合應力。也叫l(wèi)ayer transfer。

3) Smart Curt法:大家自己百度吧。

SOI的制程會帶來很多優(yōu)點,如減小短溝效應(SCE)、減小亞閾值漏電(subthreshold leakage, off-current)、提高飽和電流(on-current),所以它能提供了更高速(結電容變小)、低功耗的性能(低漏電)。當然SOI也有它固有的寄生特性:

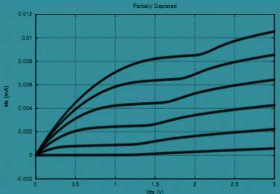

1) 最典型的為kink-effect,也叫作floating-body effect (浮體效應),因為SOI的well都是floating在substrate里面,所以它的well是沒有接電壓的,當漏極的反偏pn結流過電流時,會使硅外延層的電位提高,從而增加了溝道電導,故隨著漏電壓的增大,漏電流也增大,形成非飽和特性,從而降低了漏極擊穿電壓性能(https://en.wikipedia.org/wiki/Floating_body_effect)。而且浮體效應會導致閾值電壓的浮動、記憶效應、遲滯效應等一些列問題。當然襯底接出會解決這個問題,但是會增加面積以及增加體電阻。

2) 其次就是自加熱效應(self-heating effect),因為我們底部和周邊都是用Oxide隔離(DTI和BOX),而oxide的導熱性不好,所以載流子碰撞產生的熱量被聚集在well里,會減小載流子壽命。在Id-Vd特性曲線里飽和區(qū)曲線會略微下降,而不是微微上升。(自己google或baidu吧)

PD-SOI和FD-SOI的區(qū)別?為啥不直接用FD-SOI技術?

因為FD-SOI的開啟電壓對BOX上的Si厚度非常敏感(10mV/nm),所以在特定的領域還是會使用PD-SOI來解決Vt的variation問題。但是FD-SOI的Subthreshold亞閾值特性比PD-SOI好很多(<65mv>

現(xiàn)在很多8寸的0.18um/0.13um以下的BCD和RF制程已經開始導入SOI制程平臺或SOC (system on chip)來集成RF和高速度和低功耗特性,未來的物聯(lián)網(IoT)應該也是SOI的主流市場(無線通訊和低功耗),只是制程瓶頸在于成本和復雜度。